Understanding the constraints of using SPI protocol at high(er) frequencies

Our SPI Storm product is one of the most capable SPI host adapters on the market, with numerous options to ‘tweak’, upgrade and adapt the protocol to the user’s needs. We sometimes get the feedback that this device has an excessively broad scope in the sense that most users really look for an adapter that supports ‘just SPI’, no more, no less.

There are multiple reasons for providing an extended range of options: SPI is not a so well defined protocol and many ‘flavors’ of SPI really coexist on the market today. Another example is that – unlike a protocol like I²C – SPI does not define the clock frequency to be used. Our experience shows that the usual frequencies for SPI are around 10 MHz or perhaps 20 MHz. With technologies like FPGA, it is rather easy to use clock frequencies that go up to 50 MHz or even 100 MHz.

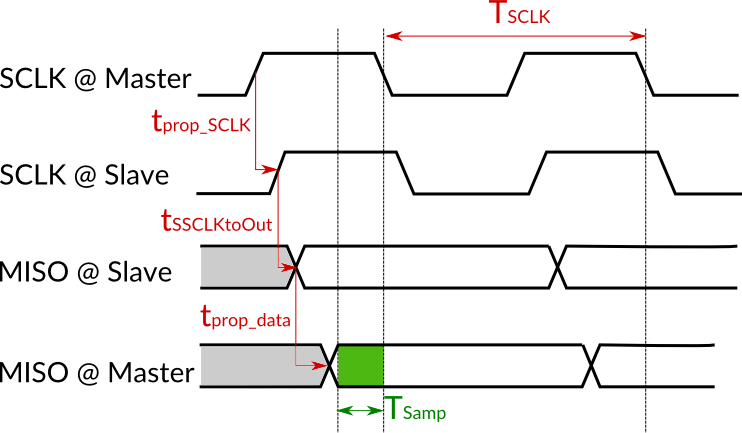

This technical paper studies the impact of increasing the clock frequencies on sampling data from the slave.